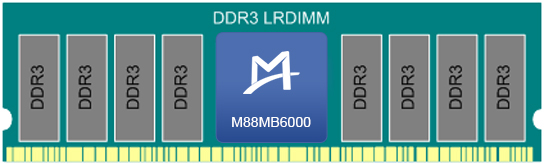

产品概述

M88MB6000是一款应用于DDR3减载双列直插内存模组(LRDIMM)的内存缓冲芯片。该芯片通过缓冲内存通道的命令、地址、控制、时钟以及数据信号,来减小内存控制器的负载和改善信号完整性,从而增加内存系统的支持容量和带宽。

M88MB6000符合JEDEC DDR3内存缓冲器标准。它最高支持速率DDR3-1866,支持单条容量高达64 GB的LRDIMM内存模组,使服务器的单机内存容量可提升到最高1536 GB。

功能特点

- 符合JEDEC DDR3内存缓冲器标准

- 最高支持速率DDR3-1866

- 寄存和重新驱动命令、地址和部分控制信号,并提供两份输出

- 双向重定时和重新驱动DDR3数据(DQ)信号

- 利用输入时钟重新生成数据选通信号(DQS)

- 生成时钟信号给内存芯片,其相位相对于输入时钟和重驱动的命令、地址和控制信号稳定,不随工艺、电压和温度变化

- 最高可支持8个物理rank

- 支持x4和x8 DRAM芯片

- 可通过SMBus读/写控制寄存器

- 内置温度传感器,可通过SMBus访问

- 可提供参考电压源给DRAM芯片

- 支持个性化字节(personality bytes)

- 超低功耗

- 支持1.5 V, 1.35 V或1.25 V的VDD电压

- 588-ball FBGA绿色封装

- 命令和地址处理

- 支持控制字写程序

- 支持对命令和地址(CA)信号的奇偶校验

- 支持CA信号的输入总线端接(IBT)

- 支持CKE功耗管理和时钟停止节省功耗模式

- 支持双频切换

- 支持软CKE模式

- 支持刷新交错

- 重新生成ODT信号给DRAM接口

- 支持列倍乘模式

- 支持地址/命令/控制信号的提前发送和延迟发送模式

- 提供4个独立的CKE信号给DRAM芯片

- 提供8个独立的片选信号(CS)给DRAM芯片

- 支持正常模式(300-1066 MHz)和测试模式(70-300 MHz)频率

- DRAM接口的驱动特性可编程配置

- 支持CA信号弱驱动模式以节省功耗

- 支持DRAM地址反转和MRS 3T定时模式

- 数据处理

- 双向的数据和数据选通DRAM内存接口

- 双向的数据和数据选通内存控制器接口

- 72个数据信号,18对差分数据选通信号

- 内置FIFO,以实现控制器和内存接口的时间域转换

- 控制器接口支持两种定时模式:最小时延和最小歪斜

- 控制器接口I/O支持标准的DDR3 DRAM规范

- 优化、低功耗的DRAM I/O接口设计

- 支持控制器接口写对平(write leveling)

- 片上校准引擎,可校准DRAM接口的读/写数据对平和DQ/DQS时序

- DFx特性

- 透明模式

- 存储器内建自测(MemBIST)

- 电压裕量测试

- 错误插入

典型应用

- 高性能DDR3服务器

- 工作站

- 网络设备

- 存储系统

- 高端桌面计算机